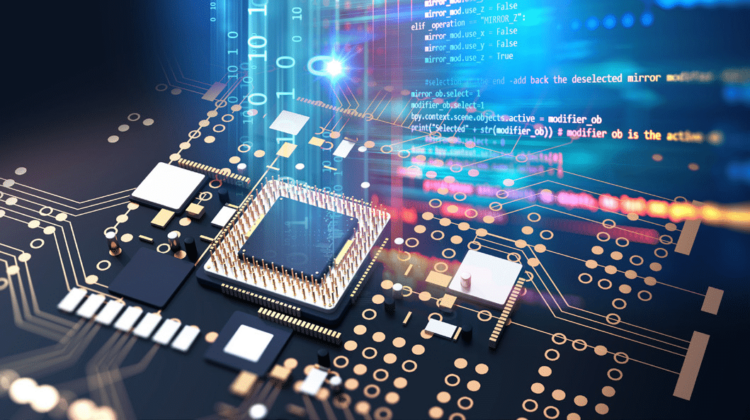

電晶體微縮一直在持續發展,但隨著製程節點不斷縮小,寄生效應增加、更高的時脈速度以及延遲上升,導致資料傳輸的能耗和延遲大幅提升。對於需要在各種系統之間傳輸大量資料的應用而言,這些成本是無法接受的。

對於高效能運算、快速通信以及大型資料中心的需求持續增長,推動了在晶片、插槽、電路板、系統及機架之間的通訊速率不斷提升。然而,隨著摩爾定律逐漸逼近極限,材料科學、晶片設計與光子技術的進步正在為高速、低功耗通訊開闢新道路。半導體與光子技術的融合帶來了典範轉移,使高頻寬、低能耗的裝置能夠無縫整合電子與光子元件。

本文將探討半導體與光子技術結合的機會與挑戰,並強調其在電信、資料中心、生物光子學和環境感測等關鍵產業中的應用。此外,還將介紹Cadence的電子/光子設計自動化(EPDA)工具如何為此轉變奠定基礎,開創高效光子積體電路(IC)設計的新道路。

理解光子技術

簡單來說,光子技術是以光子(Photon)取代電子(Electron)。它涵蓋了光子的產生、操控和偵測。在資料傳輸方面,光子技術能夠帶來數量級的速度提升,並且功耗更低,此外,它還具備在多個領域中的超靈敏感測能力。無論是在電信、製造還是醫療保健等產業,光子技術已經發揮了關鍵作用,且其應用範圍仍在不斷擴展。

光子技術與半導體的融合,進一步增強了半導體的性能。利用光子的高速與高精度特性,使電子設備變得更快速、更高效率。此外,矽光子(SiliconPhotonics)技術也被探索為光學互連的解決方案,用於取代資料中心和高效能運算系統中的傳統銅互連技術。

光子技術與半導體的融合

光子技術與半導體技術的融合,對於高效能連接的革新十分關鍵。其核心–矽光子技術,本質是透過由半導體材料製成的微小結構來控制光。這使得矽光子元件比傳統電子元件更快速、更可靠且能耗更低。

這些半導體技術的進步正在將光子技術引入晶片層級,實現光子積體電路(Photonic Integrated Circuits, PIC)。然而,與電子IC設計相比,PIC設計面臨諸多挑戰,例如訊號漂移,以及波導與互連等結構設計層面的問題。

利用Cadence加速PIC設計

PIC設計涉及獨特的布局(Layout)、錯誤檢查及電路建模等挑戰。雖然電子設計工程師擅長使用傳統的電子設計自動化(EDA)流程,但標準EDA流程無法可靠或有效地整合光子電路與電子元件。

在PIC布局裡,通常是以曲線或多邊形結構為基礎,因此這些布局往往需要手動繪製,不僅耗時且勞力密集。此外,現有的製程設計套件(PDK)尚不成熟,僅提供有限的GDS布局單元、規格與製程規則。錯誤檢查則是更艱鉅的挑戰,因為電路布局驗證(LVS)和設計規則檢查(DRC)工具仍然處於原始階段;而電路建模則因缺乏廣泛接受的SPICE等效工具,變得更加複雜。

為解決P I C 設計挑戰,益華電腦(Cadence)與業界領先的生態系統合作夥伴及晶圓代工廠攜手合作,開發了一個整合式電子/ 光子設計自動化(EPDA,Electronic/Photonic DesignAutomation)環境。

Cadence EPDA設計環境

Cadence EPDA設計環境基於業界標準的Cadence Virtuoso Studio客製化IC設計平台,支援單片整合(Monolithic)與混合式(Hybrid)設計方法,例如3DIC堆疊技術(將電子晶片置於光子晶片之上)。完整的EPDA流程涵蓋電路圖擷取(Schematic Capture)、電路模擬(CircuitSimulation),以及由電路圖驅動的布局實作(Schematic-Driven LayoutImplementation),並支援複雜光子SKILL PCells及先進的光子布局生成器(圖1)。此外,該環境還支援電子與光子元件的協同設計,以實現高效的混合系統開發。